Ddr4 оперативная: Фарпост — доска объявлений

Содержание

Есть ли жизнь в hi-end сегменте? / Хабр

Уже неоднократно рассматривался вопрос о целесообразности перехода на новое поколение оперативной памяти. К огромной радости большинства пользователей, DDR4 внедрили только на платформе Intel Socket 2011-3, поэтому только настоящие фанаты железа и энтузиасты озадачились правильным выбором оперативной памяти этого стандарта. Что купить из того, что есть на рынке? Может быть выбрать штатную частоту поменьше, да разогнать побольше? Предлагаю посмотреть на комплект памяти от ADATA — штатные частоты не заоблачные — DDR4-2400, но это ли предел?

Заморачиваться описанием внешнего вида, как обычно, я не стану, вот пара фоток — профиль, анфас, упаковка.

Отмечу средней высоты радиаторы на оперативной памяти, что приносит некоторые неудобства в плане совместимости с процессорными кулерами. Хотя, по-хорошему, при покупке столь недешевой и производительной платформы многие наверняка озадачились покупкой системы жидкостного охлаждения, а в таком раскладе, проблема высоты радиаторов неактуальна.

Под радиаторами обнаружились чипы производства SKHynix из серии MFR. Статистика по этим чипам позволяет рассчитывать на вполне приличные результаты разгона и оптимизации таймингов.

Перейдем к сути вопроса:

Тестовый стенд:

- Intel Core i7-5960X

- ASUS Rampage V Extreme, Intel X99 Socket

- OCZ Vector SSD 240 Gb

- NVIDIA GeForce 7600GT

- Corsair AX1200i

Памяти в сравнении будет два комплекта: уже описанный ADATA XPG Z1 и Corsair Vengeance DDR4-2800. Почему именно такой выбор? Очень просто — планки памяти набраны на одинаковых чипах, а стоят более чем разных денег (именно 2400 в продаже по Маркету еще нет, но есть 2133 МГц, и судя по newegg.com их цена примерно равна =) Отсюда возникает вопрос — и так недешево, так может сэкономить хоть маленько?

Задача следующая:

- Проверить сможет ли ADATA XPG Z1 DDR4-2400 CL16 работать на частоте 2800 МГц с таймингами 16-18-18-36 (именно таков номинал более дорого комплекта Corsair)

- Проверить насколько низкими могут быть тайминги для работы на частоте 2400 МГц

Что использую для проверки стабильности и производительности:

- Стабильность — тест HyperPi 0.

9.9b — многопоточный расчет числа Пи до 32 миллионного знака после запятой — вылавливает ошибки по памяти на “раз-два-три”.

9.9b — многопоточный расчет числа Пи до 32 миллионного знака после запятой — вылавливает ошибки по памяти на “раз-два-три”. - Производительность — Cinebench R15 и AIDA64 bandwidth тест — тесты рендеринга и пропускной способности памяти.

Итого на выходе должно получиться 3 графика по 4 столбика в каждом — номинал ADATA, разгон ADATA, понижение таймингов ADATA и номинал Corsair.

Приступлю к разгону памяти. С наскоку взять частоту 2800 МГц не удалось, несмотря на то, что в материнской плате ASUS Rampage V Extreme есть готовый профиль настроек для планок с такими чипами.

“Ну что же, придется повысить напряжение… Опасно? Конечно, опасно. Но, риск, как говорится,…” (С) Иван Васильевич меняет профессию.

В итоге память заработала на частоте 2800 МГц, но напряжение питания составляло 1,425В вместо штатных 1,2В. ИМХО, вполне допустимо, всего 19 процентов превышение. Теоретический нагрев чипов памяти вполне компенсируется установленными радиаторами. Память, по тактильным ощущениям, не стала больше греться.

Память, по тактильным ощущениям, не стала больше греться.

При фиксированной частоте 2400 МГц и питании 1,4125В удалось понизить тайминги до 13-16-15-39-2T.

Ну давайте сводить картинку воедино

Производительность в номинале отличается от разогнанного состояния примерно на 2 процента… Стоит ли овчинка выделки? Решайте сами. Результат в разгоне и номинал Corsair расходятся меньше чем на полпроцента. Понижение таймингов позволяет отвоевать еще полтора процента. На выходе получаем разницу между максимальным и минимальным результатом — 4 процента…. маловато получается.

Есть бонус в другом: разумеется надо посмотреть и в игрушках. Парадоксальным образом, World Of Tanks адекватно реагирует на все, что связано с повышением частоты. Недаром идеальным процессором для этой игры называли Intel Pentium G3258 с разблокированным множителем. Недорого и можно ощутимо поднять множитель при разгоне. Вот и здесь ситуация схожая. Видеокарту для теста видео я заменил на AMD Radeon R9 290X — разница между двумя режимами DDR4-2400 и DDR4-2800 составила 10 процентов, а если в абсолютных значениях — то 92 и 101 кадр в секунду соответственно. Соглашусь сразу с ораторами, которые мне скажут — мол и так больше 90 fps, чего ж еще выдумывать. Да, действительно, но факт остается фактом.

Соглашусь сразу с ораторами, которые мне скажут — мол и так больше 90 fps, чего ж еще выдумывать. Да, действительно, но факт остается фактом.

Выводы:

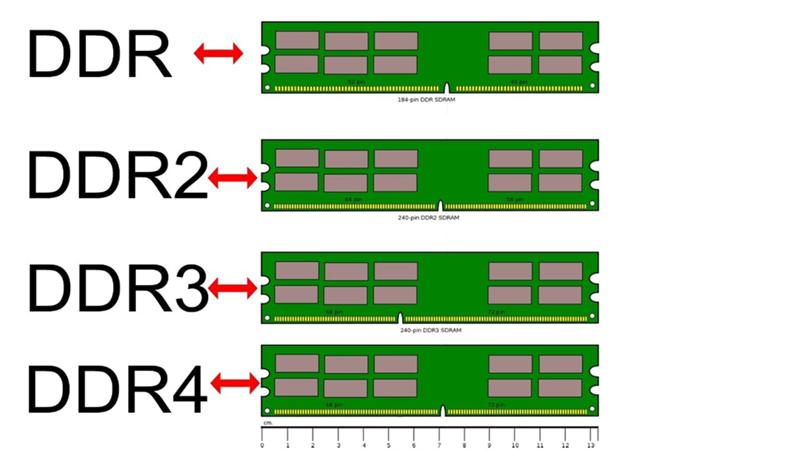

Во-первых, DDR4 только появляется на рынке и устанавливается только на одну платформу, поэтому сейчас к выбору подходят очень придирчиво.

Во-вторых, если не видно разницы, зачем платить больше? Модули, собранные на одних чипах, работают примерно одинаково, несмотря на разную маркировку. Поэтому достаточно изучить профильные форумы и сайты для того, чтобы понять — какая память оптимально подойдет по характеристикам и не будет космической по цене. Здесь ADATA XPG Z1 проявляет себя с выгодной стороны.

Я собрал ПК за 132 000 ₽

Этот текст написан в Сообществе, в нем сохранены авторский стиль и орфография.

Алексей Шапошников

Профиль автора

Причина и сроки самостоятельной сборки

Когда мне было 10 лет отец подарил на новый год ПК — «Пентиум» 4, 256 Мб оперативки, остальное не помню. Пользовался им до 18 лет, начал работать на флоте и купил себе ноутбук — характеристики особо не помню: HP на «Радионе», который сгорел. После него нет желания пользоваться ни HP, ни Радионом.

Пользовался им до 18 лет, начал работать на флоте и купил себе ноутбук — характеристики особо не помню: HP на «Радионе», который сгорел. После него нет желания пользоваться ни HP, ни Радионом.

Следующим ноутбуком был Acer i5, GeForce 880m, 6 Gb оперативки и 1 Tb жесткий диск. Прекрасный ноутбук, работает до сих пор, самое интересное — ни разу не переустонавливал «Виндоус», хотя на прошлых делал это регулярно. Пока пользовался ноутбуками мечтал купить ПК.

Долго думал и мечтал, новости о мобилизации подтолкнули на мысль, что жизнь может быть короче, чем я думал. Компьютер нужен для игр и их записи на «Ютуб». Играю во все, за что зацепится глаз — на данный момент в Evil West.

Период сборки

Начал собирать в конце сентября, заказал часть товара в DNS, часть онлайн трейд. Все приехало, купил термопасту, пришел домой и вместе с «Ютубом» собрал все за несколько часов.

Список железа и комплектующих

Я собрал ПК за 132 000 Р — из них 92 000 Р за системник, 5000 Р за мышку, 5000 Р за клавиатуру, 5000 Р за наушники, 25 000 Р за монитор. Цены округлил в небольшой плюс.

Цены округлил в небольшой плюс.

Главное требование было — чтобы тянул новые игры желательно на максималках. Информацию искал в интернете, зашел в одну группу попросил помощи в сборке ПК за 90 000 Р, в комментариях люди писали свои варианты, а я смотрел информацию про детали на «Ютубе». В итоге выбрал:

— процессор Intel i5 12400f

— видео карта kfa2 Geforce Rtx 3060 12 gb

— оперативная память patriot 3733 32 gb

— материнская плата msi pro b660 m-a ddr4 (lga 1700 mATX)

— кулер ID cooling se-214

— память SSD adata 256 gb

— еще память SSD adata m2 1tb

— Блок питания xpg pylon 750 w

— корпус Cooper Master Master box mb311l

Впечатления от собранного ПК и планы на будущее

На мой взгляд работает отлично, в разрешении 2К Cyberpunk 2077 на ультра выдает 49 FPS, Evil West — 121 FPS, остальные не смотрел.

Видео весом в 10 Гб в 1080p рендерит около 30 минут.

Плюсы и минусы сборки

Главный плюс, что все сделал сам и есть теперь небольшое понимание о самом ПК.

Минус в том, что при сборке были моменты паники, очень много похожих маленьких проводов, но главное — все внимательно читать на плате и на шнуре. Еще несколько дней постоянно смотрел температуру цп, карты, сильно переживал, что что-то сделал не так. Но оно того стоит.

Сложности и советы

Постоянно смотрел на название комплектующих в онлайн магазине, бывало отличалась одно буква, к примеру GeForce RTX 3060 EX и GeForce RTX 3060 X, я не понимал — это разные карты или в магазине ошибка. Нашел обзор на X, сравнил характеристики с Ex: почти одинаковые но Х чуть лучше, в итоге приехала именно X.

А так очень интересно, но пока собирал моментами думал, что надо было дать человеку 2500 Р и не париться.

Читатели собирают компьютеры.Истории о том, как собрать ПК самостоятельно

Поделиться опытом

DDR4 SDRAM — Понимание основ

Введение

DDR4 SDRAM очень распространены в устройствах, использующих ASIC и FPGA. В этой статье мы рассмотрим основы.

В этой статье мы рассмотрим основы.

- Как DDR4 SDRAM выглядит внутри

- Что происходит во время основных операций, таких как ЧТЕНИЕ И ЗАПИСЬ, и

- Высокоуровневое изображение подсистемы SDRAM, то есть то, что нужно вашей ASIC/FPGA для взаимодействия с памятью DDR4 SDRAM

Физическая структура

Хорошо бы начать с рассмотрения некоторых основных IO и понимания их функций. Оттуда мы погружаемся глубже, пока не доберемся до основного блока, из которого состоит память DRAM.

Верхний уровень

Как и следовало ожидать, DRAM имеет входы синхронизации, сброса, выбора микросхемы, адреса и данных. В приведенной ниже таблице немного больше подробностей о каждом из них. Это не полный список IO, здесь перечислены только основные. Потратьте немного времени, чтобы внимательно прочитать, что делает каждый ввод-вывод, особенно входы с двойным назначением адреса.

Рисунок 1: Верхний уровень

| Символ | Тип | Функция |

|---|---|---|

| СБРОС_n | Ввод | DRAM активна, только когда этот сигнал ВЫСОКИЙ |

| CS_n | Ввод | Память смотрит на все остальные входы, только если это НИЗКИЙ уровень. |

| СКЕ | Ввод | Часы включены. HIGH активирует внутренние тактовые сигналы, входные буферы устройства и выходные драйверы. |

| CK_t/CK_c | Ввод | Дифференциальные тактовые входы. Все сигналы адреса и управления отбираются при пересечении положения CK_t и отрицательного края CK_n. |

| ДК/ДКС | Вход | Шина данных и строб данных. Вот как данные записываются и считываются. Строб, по сути, является флагом достоверности данных. |

| RAS_n/A16 CAS_n/A15 WE_n/A14 | Ввод | Это входы двойного назначения. Когда ACT_n и CS_n имеют НИЗКИЙ уровень, они интерпретируются как биты адреса строки. Когда ACT_n имеет ВЫСОКИЙ уровень, они интерпретируются как командные контакты для указания команд READ, WRITE или других. |

| ACT_n | Ввод | Активировать ввод команды |

| БГ0-1 ВА0-1 | Ввод | Банковская группа, Адрес банка |

| А0-13 | Ввод | Адресные входы |

BankGroup, Bank, Row, Column

Изображение верхнего уровня показывает, как DRAM выглядит снаружи. Идя на уровень глубже, память организована так — в Bank Groups и Banks.

Рисунок 2: Банковская группа и банк

На READ из памяти вы указываете адрес, а на WRITE на него вы дополнительно предоставляете данные. Этот адрес, предоставленный вами, пользователем, обычно называется «логический адрес» . Этот логический адрес преобразуется в физический адрес до того, как он будет представлен DRAM. физический адрес состоит из следующих полей:

физический адрес состоит из следующих полей:

- Банковская группа

- Банк

- Ряд

- Колонна

эти отдельные поля затем используются для определения точного местоположения в памяти для чтения или записи.

Спустившись на следующий уровень, вы увидите вот что в каждом Банке.

- Массивы памяти

- Декодер строк

- Декодер столбцов

- Усилители чувств

Рисунок 3: Декодирование строки и столбца

После определения группы банков и банка часть адреса Строка активирует строку в массиве памяти. Это называется «Линия слов» , и при ее активации данные из массива памяти считываются в нечто, называемое «Усилители чувств» . Затем адрес столбца считывает часть слова, которое было загружено в Sense Amps. Ширина столбца называется «Битовая строка» .

Ширина столбца является стандартной — она составляет 4 бита, 8 бит или 16 бит, и DRAM классифицируются как x4, x8 или x16 в зависимости от этой ширины столбца. Следует также отметить, что ширина шины данных

Следует также отметить, что ширина шины данных DQ такая же, как ширина столбца. Итак, для упрощения можно сказать, что DRAM классифицируются на основе ширины шины DQ .

[ Боковое примечание: x16 устройства имеют только 2 группы банков, тогда как x4 и x8 имеют 4 шт., как показано на рис. 2.]

Время аналогии: Микросхема DRAM эквивалентна зданию, полному картотеки

Банковская группа Идентифицирует этаж

Адрес банка Идентифицирует картотеку на этом этаже, где находится нужный вам файл

7 Адрес строки Указывает, в каком ящике шкафа находится файл. Считывание данных в усилители считывания эквивалентно открытию/выдвижению ящика для файлов.

Col Address Идентифицирует номер файла в этом ящике

На самом низком уровне бит представляет собой конденсатор, удерживающий заряд, и транзистор, действующий как переключатель.

Рисунок 4: Битовый уровень

Поскольку конденсатор разряжается с течением времени, информация в конечном итоге исчезает, если конденсатор не периодически ОБНОВЛЕНИЕ ed. Отсюда и буква «D» в DRAM — она означает 9.0122 Dynamic в отличие от SRAM (статической оперативной памяти).

Подписаться

Получайте уведомления, когда публикуется новая статья!

Размеры и адресация DRAM

DRAM бывают стандартных размеров, что указано в спецификации JEDEC. JEDEC — это комитет по стандартам, который определяет дизайн и дорожную карту памяти DDR. Это из раздела 2.7 спецификации DDR4 JEDEC (JESD79-4B).

Рисунок 5: Адресация

Расчет размера DRAM 915 = 32К

Количество бит адреса столбца: A0-A9 = 10 бит

Количество столбцов в строке = 1K

Ширина каждого столбца = 8 бит

Количество банковских групп = 4

Количество банков = 4

Общая емкость DRAM =

Кол-во строк x

Кол-во столбцов x Ширина столбца x

Количество банковских групп x количество банков

Общая емкость DRAM =

32K x 1K x 8 x 4 x 4 =

4Gb

Размер страницы DRAM

В приведенной выше таблице упоминается Размер страницы . Размер страницы — это, по сути, количество битов в строке. Или, другими словами, это количество битов, загружаемых в Sense Amps при активации строки. Поскольку адрес столбца имеет ширину 10 бит, на строку приходится 1 КБ битовых строк. Таким образом, для устройства x4 число битов составляет 1K x 4 = 4K бит (или 512 байт). Точно так же для устройства x8 это 1 КБ, а для x16 — 2 КБ на страницу.

Размер страницы — это, по сути, количество битов в строке. Или, другими словами, это количество битов, загружаемых в Sense Amps при активации строки. Поскольку адрес столбца имеет ширину 10 бит, на строку приходится 1 КБ битовых строк. Таким образом, для устройства x4 число битов составляет 1K x 4 = 4K бит (или 512 байт). Точно так же для устройства x8 это 1 КБ, а для x16 — 2 КБ на страницу.

Ранг (Каскадирование глубины)

При работе с DRAM вы столкнетесь с такой терминологией, как одноранговая, двухранговая или четырехранговая. Ранг является высшей логической единицей и обычно используется для увеличения объема памяти вашей системы.

Допустим, вам нужно 16 ГБ памяти. В зависимости от того, что доступно на рынке и что дешевле, у вас может быть один кристалл памяти 16 ГБ, в этом случае вы бы назвали его системой с одним рангом, потому что вам просто нужен 1 сигнал ChipSelect (CS_n), чтобы прочитать все содержимое памяти. . Или вы можете припаять к печатной плате 2 отдельных дискретных устройства 8Gb (поскольку устройства 2x8Gb дешевле, чем 1x16Gb). В этом случае 2 устройства будут подключены к одному и тому же адресу и шинам данных, но вам потребуется 2 ChipSelects для отдельной адресации каждого устройства. Поскольку вам нужно два ChipSelect, эта установка называется Dual-Rank.

В этом случае 2 устройства будут подключены к одному и тому же адресу и шинам данных, но вам потребуется 2 ChipSelects для отдельной адресации каждого устройства. Поскольку вам нужно два ChipSelect, эта установка называется Dual-Rank.

[ Примечание: Еще одна разновидность DRAM, с которой вы можете столкнуться, — это «Dual-Die Package» или DDP. В этом случае у вас будет одна микросхема DRAM, припаянная к плате, но внутри упаковки она будет иметь стопку из двух кристаллов. Каждая матрица снова будет иметь общий адрес и линии данных, но будет иметь отдельный выбор чипа, что делает его двухранговым устройством.]

чип х8. Затем вы можете выбрать одно устройство x8 8 Гбит/с или два устройства x4 4 Гбит/с и соединить их «каскадом по ширине» на печатной плате. При каскадировании по ширине обе DRAM подключаются к одной и той же шине ChipSelects, Address и Command, но используют разные части шины данных (DQ и DQS). На картинке ниже первая x4 DRAM подключена к DQ[3:0], а вторая — к DQ[7:4].

Рисунок 7: Каскадирование ширины DRAM

Доступ к памяти

- Операции чтения и записи в память DDR4 SDRAM ориентированы на пакетную обработку. Он начинается в выбранном месте (в соответствии с предоставленным пользователем адресом) и продолжается в течение восьми пакетов или «прерывистого» пакета из четырех.

- Операции чтения и записи выполняются в два этапа. Он начинается с команды ACTIVATE (ACT_n и CS_n становятся НИЗКИМИ для тактового цикла), за которой затем следует команда RD или WR.

- Биты адреса, зарегистрированные одновременно с командой ACTIVATE, используются для выбора BankGroup, Bank и Row для активации (BG0-BG1 в x4/8 и BG0 в x16 выбирают группу банков; BA0-BA1 выбирают банк; A0-A17 выбирают ряд). Этот шаг также называется RAS — строб адреса строки .

- Биты адреса, зарегистрированные одновременно с командой чтения или записи, используются для выбора местоположения начального столбца для пакетной операции.

Этот шаг также называется CAS-9.0122 Строб адреса столбца.

Этот шаг также называется CAS-9.0122 Строб адреса столбца. - В каждом банке есть только один набор Sense Amps. Прежде чем можно будет выполнить чтение/запись в другую строку в том же банке, текущая открытая строка должна быть деактивирована с помощью команды PRECHARGE. ПРЕДВАРИТЕЛЬНАЯ ЗАРЯДКА эквивалентна закрытию текущего ящика с файлами в кабинете, это приводит к тому, что данные в Sense Amps записываются обратно в строку.

- Вместо выполнения явной команды PRECHARGE для деактивации строки можно использовать команды RDA (чтение с автоматической предварительной зарядкой) и WRA (запись с автоматической предварительной зарядкой). Эти команды предписывают DRAM автоматически деактивировать/предварительно зарядить строку после завершения операции чтения или записи. Поскольку адрес столбца использует только биты адреса A0-A9, A10, который является неиспользуемым битом во время CAS, перегружен, чтобы указать Auto-Precharge.

Таблица истинности команд

Я постоянно имею в виду то, что называется «командами» — команда ACTIVATE , команда PRECHARGE , команда READ , команда WRITE . Но на самой первой картинке этой статьи нет ввода «Команды» в DRAM. Так как же выдаются эти команды?

Но на самой первой картинке этой статьи нет ввода «Команды» в DRAM. Так как же выдаются эти команды?

Итак, DRAM интерпретирует ACT_n, RAS_n, CAS_n и WE_n 9.0119 вводит как команды на основе приведенной ниже таблицы истинности.

| Функция | Шорткод | CS_n | ACT_n | РАН_н/А16 | CAS_n/A15 | WE_n/A4 | А10/АП |

|---|---|---|---|---|---|---|---|

| Обновление | № | л | Х | л | л | Х | H или L |

| Предоплата одного банка | ПРЕД | л | Х | л | Х | л | л |

| Банк Активировать | АКТ | л | л | Адрес строки | |||

| Запись | ВР | л | Х | Х | л | л | л |

| Запись с автоматической предварительной зарядкой | ВРА | л | Х | Х | л | л | Х |

| Чтение | РД | л | Х | Х | л | Х | л |

| Чтение с автоподзарядкой | РДА | л | Х | Х | л | Х | Х |

Таблица истинности частичной команды

Приведенная выше таблица представляет собой лишь подмножество команд, которые вы можете использовать для DRAM. Полная таблица истинности команд DDR4 указана в разделе 4.1 спецификации JEDEC JESD79.-4Б.

Полная таблица истинности команд DDR4 указана в разделе 4.1 спецификации JEDEC JESD79.-4Б.

Чтение

Рисунок 8: Операция ЧТЕНИЕ

На рис. 8 показана временная диаграмма операции READ с длиной пакета 8 (BL8) .

- Первым шагом является команда

ACT. Значение на адресной шине в это время указывает адрес строки. - На втором этапе выдается

RDA(Чтение с автоматической предварительной зарядкой). Значение на адресной шине в это время является адресом столбца. - Команда RDA сообщает DRAM автоматически

PRECHARGEбанка после завершения чтения

Запись

Рисунок 9: Операция WRITE

На Рисунке 9 показана временная диаграмма операции WRITE .

- Первый шаг активирует строку

- Затем выдаются 2 команды

WRITE. Первый на адресCOL, а второй наCOL+8.

- Вторая операция записи не требует

ACTперед ним, потому что строка, которую мы собираемся записать, уже активна в Sense Amps - Также обратите внимание, что первая команда представляет собой простую команду

WR, поэтому строка остается активной. Вторая команда — этоWRA, которая деактивирует строку после завершения записи.

.

[ Примечание: Я кое-что спрятал сюда без особых объяснений. A16, A15 и A14 — не единственные адресные биты с двойной функцией. Команда автоматической предварительной зарядки выдается через A10, а выбор режима BurstChop4 (BC4) или BurstLength8 (BL8) выбирается через A12, если он разрешен в регистре режима.]

Подсистема DRAM

Теперь, когда мы достаточно долго обсуждали DRAM, пришло время поговорить о том, что нужно ASIC или FPGA для взаимодействия с DRAM. Это называется подсистемой DRAM и состоит из 3 компонентов:

- Сама память DRAM, включающая в себя все, что описано выше

- DDR PHY

- Контроллер DDR

Рисунок 10: Подсистема DRAM

На картинке выше многое происходит, поэтому давайте разберем ее:

- Память DRAM припаяна к плате.

Физический уровень и контроллер вместе с пользовательской логикой обычно являются частью одной и той же FPGA или ASIC.

Физический уровень и контроллер вместе с пользовательской логикой обычно являются частью одной и той же FPGA или ASIC. - Интерфейс между пользовательской логикой и контроллером может определяться пользователем и не обязательно должен быть стандартным

- Когда пользовательская логика отправляет запрос на чтение или запись контроллеру, она выдает логический адрес

- Затем контроллер преобразует этот логический адрес в физический адрес и выдает команду на PHY

- Контроллер и PHY взаимодействуют друг с другом через стандартный интерфейс, называемый интерфейсом DFI. Вы можете скачать спецификацию DFI отсюда.

- Затем PHY выполняет всю сигнализацию нижнего уровня и передает физический интерфейс в DRAM.

- Этот интерфейс между PHY и памятью указан в спецификации стандарта JEDEC JESD79-49B

.

.

Думайте о контроллере как о мозге, а о PHY как о мышцах.

- Когда вы активируете строку, вся страница загружается в Sense Amps, поэтому многократное чтение уже открытой страницы обходится дешевле, поскольку вы можете пропустить первый шаг активации строки.

Контроллер обычно имеет возможность переупорядочивать запросы, выдаваемые пользователем, чтобы воспользоваться этим преимуществом. Для переупорядочивания он использует небольшой кэш или TCAM и всегда возвращает самые последние данные, поэтому вам не нужно беспокоиться об устаревших данных или коллизиях, возникающих из-за этого переупорядочивания, выполняемого контроллером.

Контроллер обычно имеет возможность переупорядочивать запросы, выдаваемые пользователем, чтобы воспользоваться этим преимуществом. Для переупорядочивания он использует небольшой кэш или TCAM и всегда возвращает самые последние данные, поэтому вам не нужно беспокоиться об устаревших данных или коллизиях, возникающих из-за этого переупорядочивания, выполняемого контроллером. - PHY содержит аналоговые драйверы и предоставляет возможность настраивать регистры для увеличения мощности привода или изменения завершения для улучшения целостности сигнала.

В двух словах

Давай завершим это

- DRAM организована в виде банковских групп, банков, строк и столбцов

- Адрес, выданный пользователем, называется Логический адрес , и он преобразуется в физический адрес контроллером DRAM, прежде чем он будет представлен в памяти

- DDR4 классифицируются как

x4, x8 или x16в зависимости от ширины шины данныхDQ - Вы можете каскадировать глубины или ширины каскада DRAM для достижения требуемого размера

- Операции чтения и записи выполняются в два этапа.

1-й шаг активирует строку, 2-й шаг читает или записывает в память.

1-й шаг активирует строку, 2-й шаг читает или записывает в память. - Подсистема DRAM состоит из памяти, уровня PHY и контроллера

DRAM

DDR4 SDRAM Device Operation - Hynix - Каталоги в формате PDF | Техническая документация

Добавить в избранное

{{requestButtons}}

Выдержки из каталога

Функциональное описание Упрощенная диаграмма состояний из любого состояния Power Applied MPSM IVREFDQ, RTT и т. д. MRS SRX с NOP MRS SRX с NOP MRS MRS, MPR, с Q=PDA с низкой инициализацией Процедура сброса выравнивания записи ZQCL RESET Тест подключения Предварительная зарядка Выключение питания CKE_L Активное выключение питания Чтение WriteA ЧтениеA Чтение Запись WriteA ЧтениеA Автоматическая последовательность Последовательность команд Enter Power-down Exit Power-down Запись самообновления Выход из самообновления Обновление, тонкая детализация Обновление Запуск процедуры RESET Включение режима сканирования границ многоцелевого регистра ПРИМЕЧАНИЕ 1. Эта упрощенная диаграмма состояний предназначена для предоставления...

Эта упрощенная диаграмма состояний предназначена для предоставления...

Основные функции DDR4 SDRAM — это высокоскоростная динамическая память с произвольным доступом, внутренняя конфигурация которой состоит из шестнадцати банков, группы из 4 банков по 4 банка в каждой группе для x4/x8 и восьми банков, группы из 2 банков с 4 банками для каждая группа банков для x16 DRAM. DDR4 SDRAM использует архитектуру предварительной выборки 8n для достижения высокой скорости работы. Архитектура предварительной выборки 8n сочетается с интерфейсом, предназначенным для передачи двух слов данных за такт на контактах ввода-вывода. Одна операция чтения или записи для DDR4 SDRAM состоит из одной передачи данных шириной 8n бит в течение четырех тактов во внутреннем ядре DRAM...

Процедура сброса и инициализации Для включения питания и инициализации сброса, чтобы предотвратить неправильное функционирование DRAM, необходимо определить значения по умолчанию для следующих настроек MR. Режим пониженной передачи (MR3 A[3]): 0 = 1/2 скорости на адресацию DRAM (MR3 A[4]): 0 = отключить режим максимального энергосбережения (MR4 A[1]): 0 = отключить CS для управления/ Задержка адреса (MR4 A[8:6]): 000 = Отключить режим задержки проверки четности CA (MR5 A[2:0]): 000 = Отключить режим восстановления пакета жесткой записи (MR4 A[13]): 0 = Отключить программную публикацию Режим восстановления пакета (MR4 A[5]): 0 = отключить последовательность инициализации при включении питания. Следующее...

Следующее...

Статический НИЗКИЙ уровень в случае, если RTT_Nom включен в момент времени Tg, в противном случае статический ВЫСОКИЙ или НИЗКИЙ ВРЕМЯ ПЕРЕРЫВ НЕ ВАЖНО ПРИМЕЧАНИЕ 1 С момента времени «Td» до «Tk» команды DES должны применяться между командами MRS и ZQCL. ПРИМЕЧАНИЕ 2. Команды MRS должны быть отправлены во все регистры режима, для которых заданы настройки. Рисунок 1 — RESET_n и последовательность инициализации при линейном изменении при включении питания Скорость нарастания напряжения VDD при включении питания Последовательность инициализации Таблица 1 — Символ скорости нарастания напряжения VDD a. Измерение проводилось между 300 мВ и минимумом 80% Vdd. б. Измерение с ограничением полосы 20 МГц. в. Максимальное время для линейного изменения VDD от 300 мВ до VDD

Инициализация сброса при стабильном питании Следующая последовательность требуется для инициализации RESET при отсутствии прерывания питания, как показано на рис. 2. 1. RESET_n устанавливается ниже 0,2 * VDD в любое время, когда требуется сброс (все остальные входы могут быть не определены). RESET_n необходимо поддерживать для минимального tPW_RESET. CKE вытягивается как «НИЗКИЙ» до сброса RESET_n (минимальное время 10 нс). 2. Выполните шаги с 2 по 10 в разделе «Последовательность инициализации при включении питания» на стр. 8. 3. Последовательность сброса завершена, DDR4 SDRAM готова к обучению чтению/записи (включая обучение Vref и выравнивание записи). Ta VALID tXPR tZQin. .. 9TIME BREAK □ НЕ ВАЖНО ПРИМЕЧАНИЕ 1 На этой временной диаграмме показано, что режим C/A Parity Latency находится в состоянии «Disable». ПРИМЕЧАНИЕ 2 Список исключений для команд MRS, которые не относятся к tMRD - Режим пониженной передачи - Режим задержки четности C/A - Режим задержки команд/адресов CS - Режим адресации на DRAM - Значение обучения VrefDQ, режим обучения VrefDQ и диапазон обучения VrefDQ Рисунок 3 — Синхронизация tMRD Некоторые настройки регистра режима влияют на функциональность ввода адреса/команды/управления. В этом случае следующая команда MRS может быть разрешена после завершения обновления функции текущей командой MRS.

RESET_n необходимо поддерживать для минимального tPW_RESET. CKE вытягивается как «НИЗКИЙ» до сброса RESET_n (минимальное время 10 нс). 2. Выполните шаги с 2 по 10 в разделе «Последовательность инициализации при включении питания» на стр. 8. 3. Последовательность сброса завершена, DDR4 SDRAM готова к обучению чтению/записи (включая обучение Vref и выравнивание записи). Ta VALID tXPR tZQin. .. 9TIME BREAK □ НЕ ВАЖНО ПРИМЕЧАНИЕ 1 На этой временной диаграмме показано, что режим C/A Parity Latency находится в состоянии «Disable». ПРИМЕЧАНИЕ 2 Список исключений для команд MRS, которые не относятся к tMRD - Режим пониженной передачи - Режим задержки четности C/A - Режим задержки команд/адресов CS - Режим адресации на DRAM - Значение обучения VrefDQ, режим обучения VrefDQ и диапазон обучения VrefDQ Рисунок 3 — Синхронизация tMRD Некоторые настройки регистра режима влияют на функциональность ввода адреса/команды/управления. В этом случае следующая команда MRS может быть разрешена после завершения обновления функции текущей командой MRS. Команды MRS, которые не...

Команды MRS, которые не...

ПРИМЕЧАНИЕ 1. На этой временной диаграмме показано, что для режима CA Parity Latency установлено значение «Disable». ПРИМЕЧАНИЕ 2 Список исключений команд MRS, которые не применяются к tMOD — включение DLL, сброс DLL — значение обучения VrefDQ, внутренний монитор Vref, режим обучения VrefDQ и диапазон обучения VrefDQ — режим пониженной передачи — режим адресации по DRAM — режим максимального энергосбережения — Режим CA Parity Рисунок 4 — Синхронизация tMOD В некоторых случаях установки регистра режима обновление функции занимает больше времени, чем tMOD. Команды MRS, которые не применяют синхронизацию tMOD к следующей допустимой команде, за исключением DES, перечислены в примечании 2 к рисунку 9.. Эти входные команды MRS...

RTT_NOM tADC_min tADC_min tADC_max ПРИМЕЧАНИЕ 1 ПРИМЕЧАНИЕ 1 На этой временной диаграмме режим CA Parity Latency находится в состоянии «Disable». ПРИМЕЧАНИЕ 2 ПРИМЕЧАНИЕ 2 Когда команда MRS, упомянутая в этом примечании, влияет на время включения RTT_NOM, время выключения RTT_NOM и значение RTT_NOM, это означает, что значение регистра MR изменяется. Сигнал ODT должен быть установлен на низкий уровень по крайней мере в течение такта DODTLoff +1, прежде чем будет выдана затрагивающая их команда MRS, и оставаться на низком уровне до истечения времени tMOD. Следующие регистры MR влияют на время включения RTT_NOM, время выключения RTT_NOM и значение RTT_NOM, и требуют, чтобы ODT был низким, когда команда MRS...

Сигнал ODT должен быть установлен на низкий уровень по крайней мере в течение такта DODTLoff +1, прежде чем будет выдана затрагивающая их команда MRS, и оставаться на низком уровне до истечения времени tMOD. Следующие регистры MR влияют на время включения RTT_NOM, время выключения RTT_NOM и значение RTT_NOM, и требуют, чтобы ODT был низким, когда команда MRS...

SK hynix Таблица 3 — Задержка CAS

Таблица 6 — Распределение битов MR DDR4 для Rx EQ Control

ПРИМЕЧАНИЕ. 1. Преамбула записи 2 tCK действительна для DDR4-2400/2666/2933/3200 Speed Grade. Для 2-го набора из 2 преамбул записи tCK дополнительный CWL не требуется.

ПРИМЕЧАНИЕ: 1. Задержка команды записи, когда включены CRC и DM: 2. Если меньше или равно 1600, то 4nCK; ни 5nCK, ни 6nCK 3. Если больше 1600 и меньше или равно 2666, то 5nCK; ни 4nCK, ни 6nCK 4. Если больше 2666 и меньше или равно 3200, то 6nCK; ни 4nCK, ни 5nCK

Таблица 11 — Формат данных MPR ПРИМЕЧАНИЕ: 1. MPR, используемый для считывания журнала ошибок четности C/A, включается установкой A[2] в MR3 2. Для более высокой плотности DRAM, где A[17] не используется, MPR2 [1] следует рассматривать как безразличное. 3. Если устройство используется в монолитном приложении, где C[2:0] не используются, то MPR3[2:0] следует рассматривать как неважно. 4. Биты MPR3 0~2 (задержка четности CA) отражают последние запрограммированные значения задержки четности CA.

Для более высокой плотности DRAM, где A[17] не используется, MPR2 [1] следует рассматривать как безразличное. 3. Если устройство используется в монолитном приложении, где C[2:0] не используются, то MPR3[2:0] следует рассматривать как неважно. 4. Биты MPR3 0~2 (задержка четности CA) отражают последние запрограммированные значения задержки четности CA.

ПРИМЕЧАНИЕ: 1. Страница 3 MPR специально назначена DRAM. Фактический метод кодирования зависит от поставщика.

ПРИМЕЧАНИЕ: 1. Задержка четности должна быть запрограммирована в соответствии с временными параметрами таблицы скорости

.

Все каталоги и технические брошюры Hynix

Работа устройства DDR SDRAM

36 страниц

Операции с устройством DDR2 SDRAM

62 страницы

Работа устройства DDR3L SDRAM

147 страниц

DDR4 SDRAM SO-DIMM На основе 4Gb A-die

77 страниц

Флэш-память NAND

10 страниц

Мобильная память

5 страниц

Графическая память

5 страниц

Потребительская память

7 страниц

Вычислительная память

24 страницы

Каталог продукции

12 страниц

Датабук за 2013 г.

9.9b — многопоточный расчет числа Пи до 32 миллионного знака после запятой — вылавливает ошибки по памяти на “раз-два-три”.

9.9b — многопоточный расчет числа Пи до 32 миллионного знака после запятой — вылавливает ошибки по памяти на “раз-два-три”. Этот шаг также называется CAS-9.0122 Строб адреса столбца.

Этот шаг также называется CAS-9.0122 Строб адреса столбца.

Физический уровень и контроллер вместе с пользовательской логикой обычно являются частью одной и той же FPGA или ASIC.

Физический уровень и контроллер вместе с пользовательской логикой обычно являются частью одной и той же FPGA или ASIC. Контроллер обычно имеет возможность переупорядочивать запросы, выдаваемые пользователем, чтобы воспользоваться этим преимуществом. Для переупорядочивания он использует небольшой кэш или TCAM и всегда возвращает самые последние данные, поэтому вам не нужно беспокоиться об устаревших данных или коллизиях, возникающих из-за этого переупорядочивания, выполняемого контроллером.

Контроллер обычно имеет возможность переупорядочивать запросы, выдаваемые пользователем, чтобы воспользоваться этим преимуществом. Для переупорядочивания он использует небольшой кэш или TCAM и всегда возвращает самые последние данные, поэтому вам не нужно беспокоиться об устаревших данных или коллизиях, возникающих из-за этого переупорядочивания, выполняемого контроллером. 1-й шаг активирует строку, 2-й шаг читает или записывает в память.

1-й шаг активирует строку, 2-й шаг читает или записывает в память.